- HOME

- 微細加工(FIB加工)

- FIB回路修正・配線修正

FIB回路修正・配線修正

集束イオンビーム(FIB)装置により

半導体のFIB回路修正・配線修正を行います

半導体内部の回路修正・配線修正を短納期、⾼歩留まりで実施、お客様の半導体開発、製造のお⼿伝いをさせていただいております。

サービス内容

配線の接続

FIBのデポ機能によって配線同士を接続します。

配線の切断

ご指定箇所の配線を切断します。

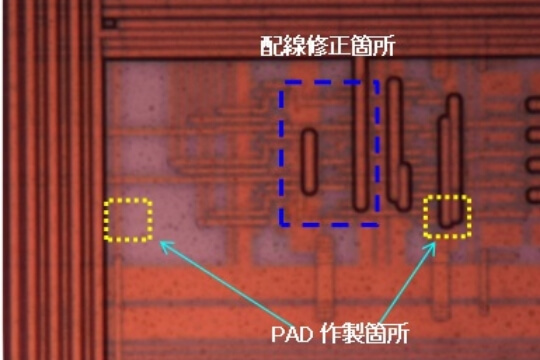

プロービングPADの作製

ご指定のサイズと形状でPADを作製します。

セイコーフューチャークリエーションのFIB回路修正・配線修正が選ばれる理由

サービス開始から35年以上の実績を持ち、高品質な技術とサービスをご提供いたします。

その1

高品質

35年以上の経験と実績により高い品質、高い成功率(高歩留)を確保します。

その2

短納期

加工技術者が直接お客様と会話をして短期仕上がり方法を選択します。

その3

手厚いフォローと最適な提案

加工技術者が直接お客様と会話してお客様の意向に沿った最適な提案をいたします。

FIB回路修正・配線修正に関するお問い合わせはこちらから

お客様のご要望に対して技術者が最適な回路修正・配線修正の加工方法を提案いたします。

お気軽にご相談ください。

回路修正・配線修正加工の流れ

STEP1

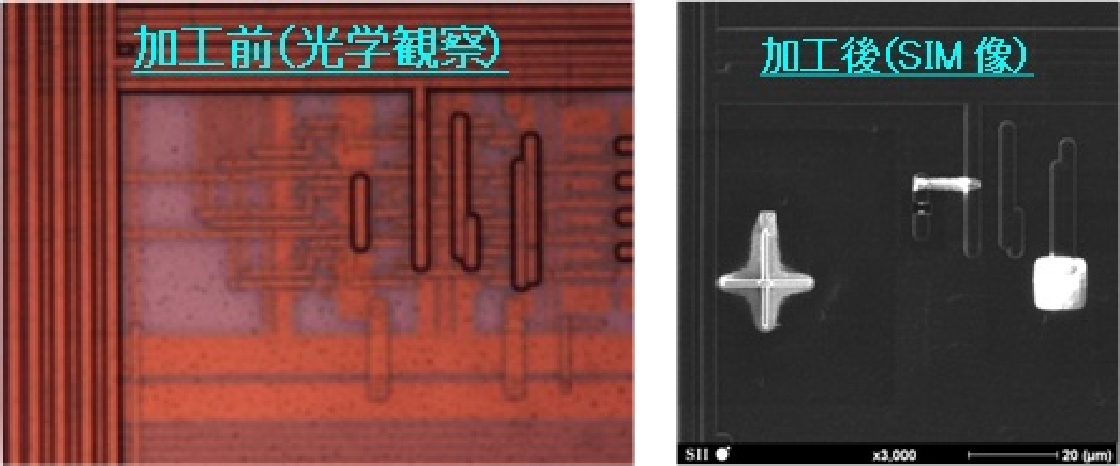

光学観察等による加工対象部の確認

事前に光学観察等で加工対象部の確認を行います。

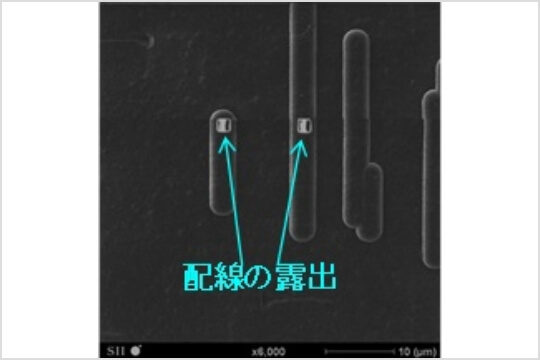

STEP2

金属配線の露出(保護膜の開口処理)

配線の表面には保護膜が存在します。

所望の配線同士を接続するためにはこの保護膜に穴を開けて、各配線を露出させる処理が必要です。

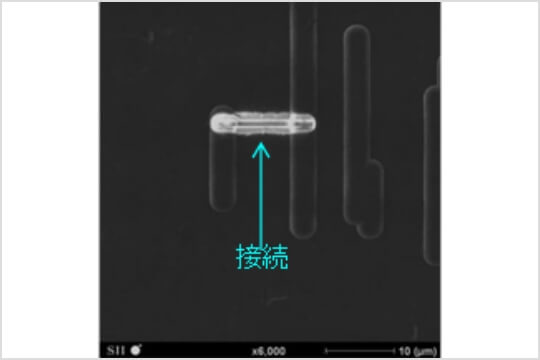

STEP3

配線の接続

FIBのデポ機能によって配線同士を接続し、新たな回路を作製します。

STEP4

配線の切断

お客様ご指定箇所の配線を切断することで、配線の修正が完成します。

オプション

プロービングPADの作製

ご指定のサイズと形状でPADを作製します

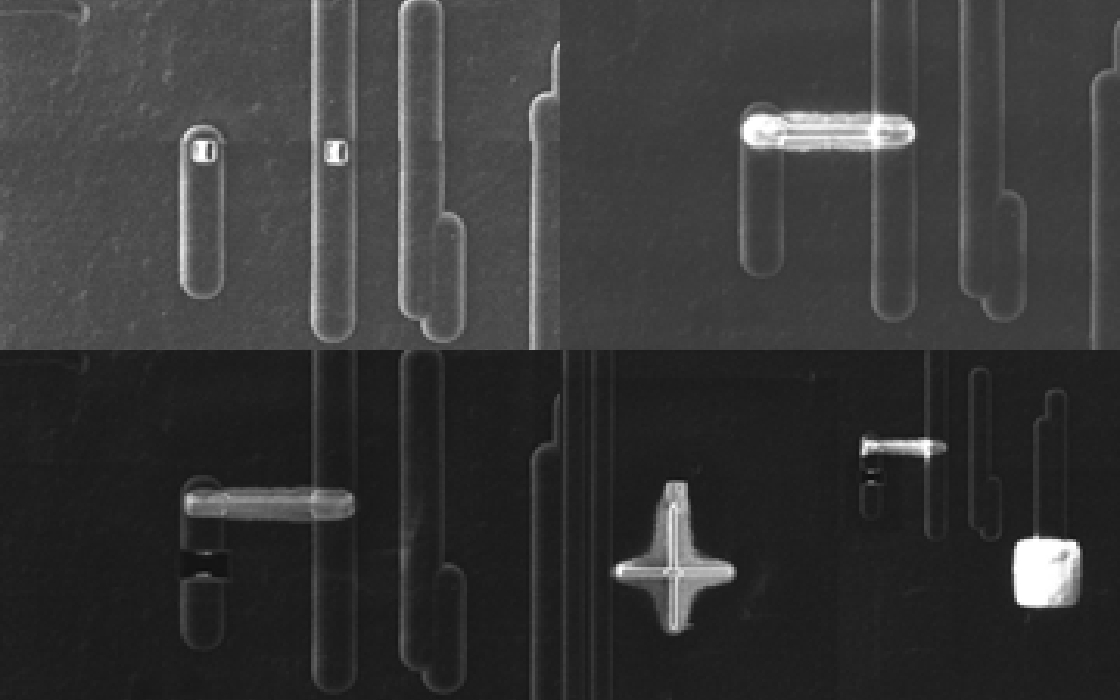

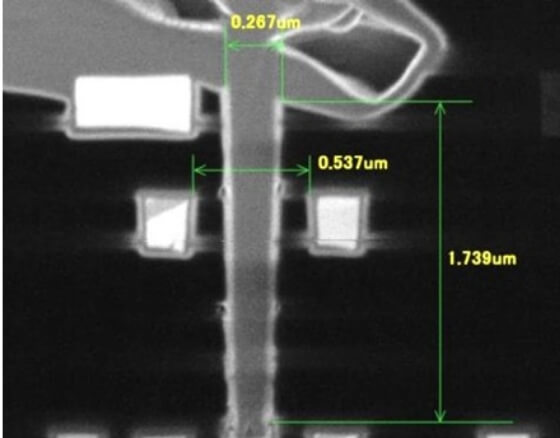

高い技術力の一例

高アスペクト・エッチング

| 加工部の観察結果 | 加工部の径:約0.3μm 加工部の到達深さ:約1.7μm アスペクト比:5.7 |

|---|---|

| 加工時のアシストガス | XeF2使用 |

FIB回路修正・配線修正に関するお問い合わせはこちらから

お客様のご要望に対して技術者が最適な回路修正・配線修正の加工方法を提案いたします。

お気軽にご相談ください。